#### Towards EXtreme scale Technologies and Accelerators for euROhpc hw/Sw Supercomputing Applications for exascale

## WP7 Dissemination, Communication and Exploitation

#### D7.4 Communication and Dissemination Report 1 (Revised Version at M24)

http://textarossa.eu

This project has received funding from the European Union's Horizon 2020 research and innovation programme, EuroHPC JU, grant agreement No 956831

#### TEXTAROSSA

#### Towards EXtreme scale Technologies and Accelerators for euROhpc hw/Sw Supercomputing Applications for exascale

Grant Agreement No.: 956831

#### Deliverable: D7.4 Communication and Dissemination Report 1

Project Start Date: 2021-04-01

Duration: 36 months

**Coordinator**: AGENZIA NAZIONALE PER LE NUOVE TECNOLOGIE, L'ENERGIA E LO SVILUPPO ECONOMICO SOSTENIBILE - ENEA , Italy.

| Deliverable No | D7.4                         |

|----------------|------------------------------|

| WP No:         | WP7                          |

| WP Leader:     | CINI-POLIMI                  |

| Due date:      | M18 (2022-09-30)             |

| Delivery date: | 2023-04-06 (Revised version) |

**Dissemination Level:**

| PU | Public                                                                                | х |

|----|---------------------------------------------------------------------------------------|---|

| PP | Restricted to other programme participants (including the Commission Services)        |   |

| RE | Restricted to a group specified by the consortium (including the Commission Services) |   |

| СО | Confidential, only for members of the consortium (including the Commission Services)  |   |

#### DOCUMENT SUMMARY INFORMATION

| Project title:                 | Towards EXtreme scale Technologies and Accelerators for euROhpc hw/Sw Supercomputing Applications for exascale |

|--------------------------------|----------------------------------------------------------------------------------------------------------------|

| Short project name:            | TEXTAROSSA                                                                                                     |

| Project No:                    | 956831                                                                                                         |

| Call Identifier:               | H2020-JTI-EuroHPC-2019-1                                                                                       |

| Unit:                          | EuroHPC                                                                                                        |

| Type of Action:                | EuroHPC - Research and Innovation Action (RIA)                                                                 |

| Start date of the project:     | 2021-04-01                                                                                                     |

| Duration of the project:       | 36 months                                                                                                      |

| Project website: TEXTAROSSA.eu |                                                                                                                |

#### WP7 Dissemination, Communication and Exploitation

| Deliverable number:     | D7.4                                    |               |               |         |           |          |

|-------------------------|-----------------------------------------|---------------|---------------|---------|-----------|----------|

| Deliverable title:      | Communica                               | ation and Dis | semination Re | eport 1 |           |          |

| Due date:               | M18                                     |               |               |         |           |          |

| Actual submission date: | 2023-04-06                              | (Revised Ver  | rsion)        |         |           |          |

| Editor:                 | Federico Re                             | ghenzani      |               |         |           |          |

| Authors:                | W. Fornaciari, G. Agosta, F. Reghenzani |               |               |         |           |          |

| Work package:           | WP7                                     |               |               |         |           |          |

| Dissemination Level:    | Public                                  |               |               |         |           |          |

| No. pages:              | 36                                      |               |               |         |           |          |

| Authorized (date):      | 2023-04-06                              |               |               |         |           |          |

| Responsible person:     | William Fornaciari                      |               |               |         |           |          |

| Status:                 | Plan                                    | Draft         | Working       | Final   | Submitted | Approved |

#### **Revision history:**

| Version | Date       | Author                                                 | Comment                                    |

|---------|------------|--------------------------------------------------------|--------------------------------------------|

| 0.1     | 2022-09-15 | F.Reghenzani                                           | Initial Draft                              |

| 0.2     | 2022-09-20 | F.Reghenzani                                           | Writing of main text                       |

| 0.3     | 2022-10-05 | F.Reghenzani                                           | Integrating partners' contribution         |

| 0.4     | 2022-10-13 | F.Reghenzani                                           | Integrating latest contributions           |

| 0.5     | 2022-10-18 | G. Agosta                                              | First review of the document               |

| 1.0     | 2022-10-21 | F. Reghenzani                                          | First complete document ready to review    |

| 1.1     | 2022-10-22 | M. Aldinucci                                           | Add "network collaboration" section        |

| 1.2     | 2022-10-23 | F. Reghenzani, W.Fornaciari Final fixes and formatting |                                            |

| 2.0     | 2023-03-10 | F. Reghenzani First editing after reviews              |                                            |

|         |            | F. Reghenzani, G. Agosta W.                            | Integration of all partners' contributions |

| 2.1     | 2023-03-30 | Fornaciari                                             |                                            |

| 2.2     | 2023-04-03 | F.Reghenzani, W.Fornaciari                             | Candidate version of the revised document  |

| 2.3     | 2023-04-06 | F.Reghenzani                                           | Final formatting                           |

#### **Quality Control:**

| Checking process               | Who                 | Date       |

|--------------------------------|---------------------|------------|

| Checked by internal reviewer   | Paolo Palazzari     | 2023-04-04 |

| Checked by Task Leader         | Federico Reghenzani | 2023-04-01 |

| Checked by WP Leader           | William Fornaciari  | 2023-03-05 |

| Checked by Project Coordinator | Massimo Celino      | 2023-04-06 |

#### COPYRIGHT

#### © Copyright by the TEXTAROSSA consortium, 2021-2024

This document contains material, which is the copyright of TEXTAROSSA consortium members and the European Commission, and may not be reproduced or copied without permission, except as mandated by the European Commission Grant Agreement No. 956831 for reviewing and dissemination purposes.

#### ACKNOWLEDGEMENTS

This project has received funding from the European High-Performance Computing Joint Undertaking (JU) under grant agreement no 956831. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Italy, Germany, France, Spain, Poland.

Please see <u>http://TEXTAROSSA.eu</u> for more information on the TEXTAROSSA project.

The partners in the project are AGENZIA NAZIONALE PER LE NUOVE TECNOLOGIE, L'ENERGIA E LO SVILUPPO ECONOMICO SOSTENIBILE (ENEA), FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG E.V. (FHG), CONSORZIO INTERUNIVERSITARIO NAZIONALE PER L'INFORMATICA (CINI), INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET AUTOMATIQUE (INRIA), BULL SAS (BULL), E4 COMPUTER ENGINEERING SPA (E4), BARCELONA SUPERCOMPUTING CENTER-CENTRO NACIONAL DE SUPERCOMPUTACION (BSC), INSTYTUT CHEMII BIOORGANICZNEJ POLSKIEJ AKADEMII NAUK (PSNC), ISTITUTO NAZIONALE DI FISICA NUCLEARE (INFN), CONSIGLIO NAZIONALE DELLE RICERCHE (CNR), IN QUATTRO SRL (in4). Linked third parties of CINI are POLITECNICO DI MILANO (CINI-POLIMI), Università di Torino (CINI-UNITO) and Università di Pisa (CINI-UNIPI); linked third party of INRIA is Université de Bordeaux; in-kind third party of ENEA is Consorzio CINECA (CINECA); in-kind third party of BSC is Universitat Politècnica de Catalunya (UPC).

The content of this document is the result of extensive discussions within the TEXTAROSSA © Consortium as a whole.

#### DISCLAIMER

The content of the publication herein is the sole responsibility of the publishers and it does not necessarily represent the views expressed by the European Commission or its services.

The information contained in this document is provided by the copyright holders "as is" and any express or implied warranties, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose are disclaimed. In no event shall the members of the TEXTAROSSA collaboration, including the copyright holders, or the European Commission be liable for any direct, indirect, incidental, special, exemplary, or consequential damages (including, but not limited to, procurement of substitute goods or services; loss of use, data, or profits; or business interruption) however caused and on any theory of liability, whether in contract, strict liability, or tort (including negligence or otherwise) arising in any way out of the use of the information contained in this document, even if advised of the possibility of such damage.

# Table of contents

| Table of c       | ontents                                                     | 5  |  |  |

|------------------|-------------------------------------------------------------|----|--|--|

| List of Figures7 |                                                             |    |  |  |

| List of Tab      | bles                                                        | 7  |  |  |

| Executive        | Summary                                                     | 8  |  |  |

| 1 Repo           | ort and Plans on Communication and Dissemination Activities | 9  |  |  |

| 1.1              | Scientific publications                                     | 9  |  |  |

| 1.1.1            | L Book                                                      | 9  |  |  |

| 1.2              | Other dissemination activities in scientific venues         | 10 |  |  |

| 1.3              | Dissemination activities toward the general public          | 10 |  |  |

| 1.4              | Networking activities                                       | 11 |  |  |

| 1.5              | Website and Social Media reports                            | 11 |  |  |

| 1.5.1            | Website privacy and analytics engine                        | 12 |  |  |

| 1.5.2            | 2 Website analytics                                         | 12 |  |  |

| 1.5.3            | 3 Social Media                                              | 15 |  |  |

| 2 Indiv          | vidual Dissemination Plans and Reports                      | 16 |  |  |

| 2.1              | ENEA                                                        | 16 |  |  |

| 2.2              | FHG                                                         | 16 |  |  |

| 2.3              | CINI                                                        | 16 |  |  |

| 2.4              | INRIA                                                       | 16 |  |  |

| 2.5              | E4                                                          | 17 |  |  |

| 2.6              | BSC                                                         | 18 |  |  |

| 2.7              | PSNC                                                        | 18 |  |  |

| 2.8              | INFN                                                        | 18 |  |  |

| 2.9              | CNR                                                         | 18 |  |  |

| 3 Indiv          | vidual Exploitation Plans and Reports                       | 20 |  |  |

| 3.1              | ENEA                                                        | 20 |  |  |

| 3.2              | FHG                                                         | 20 |  |  |

| 3.3              | CINI                                                        | 20 |  |  |

| 3.4              | INRIA                                                       | 21 |  |  |

| 3.5              | ATOS                                                        | 21 |  |  |

| 3.6              | E4                                                          | 22 |  |  |

| 3.7              | BSC                                                         | 22 |  |  |

| 3.8              | PSNC                                                        | 22 |  |  |

#### textarossa

|   | 3.9  | INFN            |

|---|------|-----------------|

|   | 3.10 | CNR             |

|   | 3.11 | InQuattro23     |

| 4 | Proc | lucts and IPs24 |

|   | 4.1  | ENEA            |

|   | 4.2  | CINI            |

|   | 4.3  | INRIA           |

|   | 4.4  | ATOS            |

|   | 4.5  | E429            |

|   | 4.6  | BSC29           |

|   | 4.7  | PSNC            |

|   | 4.8  | INFN            |

|   | 4.9  | CNR             |

|   | 4.10 | InQuattro       |

| 5 | Cond | clusions        |

| 6 | Refe | rences          |

# List of Figures

| Figure 1: Participants at the EuroHPC19 Collaboration Workshop – Madrid – Sep 2022 (from | n TEXTAROSSA: |

|------------------------------------------------------------------------------------------|---------------|

| M. Celino, M. Aldinucci, P. Palazzari)                                                   | 11            |

| Figure 2: Daily unique users as reported by GA                                           | 13            |

| Figure 3: Geographic distribution of the users                                           | 13            |

| Figure 4: How the users find the TEXTAROSSA website                                      | 14            |

| Figure 5: Most visited pages                                                             | 14            |

| Figure 6: Example of LinkedIn post by E4                                                 | 17            |

## List of Tables

No tables in the document.

## **Executive Summary**

This deliverable reports the plans to drive dissemination and exploitation of the TEXTAROSSA project and the results achieved in the first reporting period. We report the overall results achieved by the project, individual dissemination and exploitation plans undertaken by each partner. Plans are reported as an update with respect to the grant agreement. In particular, the deliverable highlights the scientific output of the project, which consisted for the first reporting period in 4 journal articles and 12 conference papers (11 published, 1 accepted), which puts TEXTAROSSA well in advance with respect to the initial plans, which foresaw a total of 5 journal articles and 15 conference paper during the entire span of the project. Regarding the exploitation path, and define the role that each partner will play. Furthermore, we identify the exploitable results of the project in terms of its innovation products. Then, we report the plans set by each partner to exploit its innovation products, as well as the results of any action already carried out during the first reporting period.

Section 3 has been updated and it worth noticing that CINI-UNITO will purchase a E4 server based on the TEXTAROSSA technology, that will be located in the green datacenter of CINI-UNITO for wider testing with the existing commercial users and to foster further scientific cooperation with the project partners.

Section 4 has been added to cover aspects related to the Innovations and IPs, hence contributing to meet the specific recommendations contained in the Review Report of the first reporting period.

# 1 Report and Plans on Communication and Dissemination Activities

The dissemination activities of the TEXTAROSSA project can be split into scientific publications, other dissemination activities (talk, presentations, general public dissemination, etc.), networking activities, and web-related dissemination (such as the website and social media). In the following sections, we will report the current status of dissemination activities until M18 of each of the mentioned categories.

## 1.1 Scientific publications

At the date of writing of this deliverable, the consortium published a total of 4 international journal articles and 11 conference papers related to the TEXTAROSSA project (in addition to 1 conference paper accepted but not published yet). The list of publishers of the published articles is as follows:

- IEEE: 1 journal article, 1 conference paper

- ACM: 1 conference paper

- Elsevier: 3 journal articles

- Springer: 5 conference papers

- Other publishers: 4 conference papers

The goal for publications in the grant agreement and D7.3 is 5 journal publications, 15 conference papers, and 1 book plan. At M18, halfway for the project, **the consortium already achieved the 80% of the goals** for publications in journal articles and conference papers categories. We expect to comfortably reach the goal and probably surpass it by a good amount, thanks to the future publications that are expected to be more numerous thanks to the increasing availability of new data as the project further proceed. The full list of the published papers is regularly updated and available on the website (<u>https://textarossa.eu/dissemination/publications/</u>).

A special mention is for the conference paper at Euromicro Conference on Digital System Design (DSD) conference [1] and the derived journal article in Microprocessors and Microsystems [2] that present the project and its goals to the scientific community. The conference paper has been presented at the conference Digital System Design (DSD) in Palermo, Italy (moved to virtual due to COVID'19).

In accordance with the open access requirements of Article 29.2, all the articles either have been published with an open access policy (gold open access) or an authors' version has been published in institutional repositories.

#### 1.1.1 Book

Task T7.2 (M1-M36) has the goal to prepare a book proposal to be submitted to a publisher 6 months after the end of the project. A full proposal is expected only at a later stage of the project when more results and publications are available. In this initial phase of the task T7.2, by looking at the preliminary results, we identified the main topics, which may be mapped in the future to book chapters: thermal management, mixed-precision computing, and hardware/software co-design. Other research projects showed interest in a joint book proposal, and we are evaluating such a possibility.

## 1.2 Other dissemination activities in scientific venues

In addition to the scientific publications above, the following presentations have been made in the context of the TEXTAROSSA project in scientific venues:

- 1. Prof. William Fornaciari (CINI-POLIMI) presented an overview of the project and a description of a specific technology, in the keynote "Design of secure power monitors for hardware accelerators", given at the Conference SAMOS 2022, Samos, Greece, July 6th, 2022.

- 2. Prof. William Fornaciari (CINI-POLIMI) presented the project with a talk entitled "Design of secure power monitors for accelerators, by exploiting ML techniques, in the Euro-HPC TEXTAROSSA project" at the SCADL workshop co-located with IPDPS conference, June 2022.

- 3. Dr. Giuseppe Zummo (In Quattro) presented "Innovative Two-Phase Cooling Solutions for the Exascale Computing Systems" at ISC High Performance Conference, May 2022.

- 4. Dr. Alessandro Lonardo (INFN) presented the TEXTAROSSA project at the annual INFN Workshop on Computing, May 2022.

- 5. Dr. Francesco Simula (INFN) presented "Distributed and Plastic Spiking Neural Network model of the brain cortex behavior" at PSNC Internal Seminars Series, February 2022.

- 6. Dr. Iacopo Colonnelli (CINI-UNITO) presented "Hybrid Workflows For Large-Scale Scientific Applications" at 6th EAGE High Performance Computing Workshop, Sep. 2022.

- 7. Dr. Iacopo Colonnelli (CINI-UNITO) presented "Hybrid workflows for heterogeneous distributed computing" at 3rd Italian Workshop on HPC (ITWSHPC), Torino, Italy, Sep. 2022.

- 8. Prof. Marco Aldinucci (CINI-UNITO) presented "From small files to no files" at 6th Workshop on Performance and Scalability of Storage Systems. Saclay, France, Jun. 2022.

- 9. Dr. Iacopo Colonnelli (CINI-UNITO) presented at the NVidia HPC round table, Bologna, Sep. 2022

- 10. Prof. Marco Danelutto (CINI-UNIPI) presented "HPC@CINI: the HPC Key technology and tools lab experience" at the ACM Computing Frontier, Torino, Italy, 2022.

In the following months, thanks to the more and more relaxed restrictions on COVID that allow the inpresence participation to conferences, we plan to sponsor the project to several scientific venues, with talks, posters and flyers.

## 1.3 Dissemination activities toward the general public

In addition to the dissemination activities delivered by the consortium members in scientific venues, prof. Marco Aldinucci (CINI-UNITO) presented the TEXTAROSSA project in the following events for general public:

- UNIGHT 2022: EU Researchers' night, Torino, Italy, September 2022.

- $\circ$  > 1000 contacts, mostly with students (secondary school, BSc, MSc).

- Lectio Magistralis at the finals of Italian Olympic Games of Informatics, Biella, Italy, September 2022.

- $\circ$  > 100 secondary school finalists to the Olympic games 2022 and their families.

- "La convergenza HPC-cloud è l'anello mancante tra il calcolo scientifico e l'IA applicate", Virtual, Sep. 2022.

- > 100 participaints from Italian SMEs.

- "Da HPC4AI al living lab dello spoke FutureHPC del Centro Nazionale HPC, Condivisioni Conferenza GARR", Palermo, Italy, Jun. 2022

> 100 participants from the community of Italian universities in the area of networking and cloud.

## 1.4 Networking activities

The consortium, in particular Prof. Marco Aldinucci (CINI-UNITO) as leader of the task T7.3 (Networking with EU HPC landscape and Centres of Excellence), participated in the following international networking events among researchers:

- EuroHPC EoCoE final summit, Napoli, Italy, Jun 2022

- ELIXIR Cloud, Data & AAI Bi-weekly Technical Calls, Virtual, 2022

- HiPEAC Vision meeting, Brussels, Belgium, May 2022

- EuroHPC summit week, Paris, France, Mar 2022

- Teratec meeeting, Saclay, France, Jun 2022

- HPC Day within "Critical Infrastructure Protection Forum CIP FORUM V 2022 Critical Infrastructure Protection & Resilience Europe 2022", Bucharest, Jun 2022

- First EuroHPC19 Workshop to Seed and Foster Collaborations Across Europe, Madrid, Spain, Sep. 2022

Figure 1: Participants at the EuroHPC19 Collaboration Workshop – Madrid – Sep 2022 (participants in TEXTAROSSA: M. Celino, M. Aldinucci, P. Palazzari)

## 1.5 Website and Social Media reports

All the journal articles, conference papers, and presentations published and presented by the consortium have been published on the website in the "Publications" page. All the papers have been published either in gold open access (so freely accessible via the editor website) or with green open access (editor version is closed and requires a fee, while an author's version is freely available through institutional repositories). In the "Publications" page, to each article is indicated the Digital Object Identifier and the relative link, in addition to a link to the pre-print version of the article if published in green open access.

At the date of writing, the consortium has published seven blog posts on the website, containing general information on the status of the research project. These have been authored by ATOS, INRIA, ENEA, INFN, CNR, and CINI. These blog posts have the goal to maintain active the website and increase the dissemination to the general public, also with reposting on social media. As the project advances, more blog posts are expected in the future, and a monthly-based publishing plan has been prepared involving all the partners.

In addition to the blog posts, news about project events and general updates are also published on the website. For instance, we reported the experiments, with the relative photos, of the new two-phase cooling system by InQuattro and CINI-POLIMI (link).

#### 1.5.1 Website privacy and analytics engine

In D7.2 Section 1.2, we explained that Google Analytics<sup>®</sup> (GA) was selected as the analytics platform for the website with the goal to measure the audience and, in general, the performance of the dissemination activities of TEXTAROSSA via the website. However, on June 23, 2022, the Italian privacy regulator agency (Garante della Privacy) issued a notice declaring the use of GA non-compliance with GDPR, due to the data transfer to the United States, having less strict privacy protections. In consequence, being the server hosted by CINI-POLIMI in Italy, we have been forced to remove GA from the TEXTAROSSA website and replace it with a compliant solution.

The website is hosted by POLIMI on own servers. After we have been informed of the regulatory agency notice, we set up an on-premises analytics server exploiting the open-source software Matomo (<u>https://matomo.org/</u>). The server is hosted in Italy, precisely at the Department of Electronics, Information and Bioengineering of POLIMI. All the necessary privacy configuration and security measures have been put in place, according to GDPR. To optimize the computing resources, the server has also been subsequently made available to other H2020 projects and department websites.

The new analytics server provides the same functionality as GA, without violating the GDPR rules. To retroactively comply with the GDPR, we moved all the data out from GA and stored all the data on Italian servers. The GA account and all the users' data have been deleted. Due to the need for an immediate stop of the use of GA and the time needed to set up the new analytics platform, we lost the analytics data from July 7 to July 10 and due to technical issues from August 15 to August 30.

#### 1.5.2 Website analytics

In this section, we show the data analytics of the website as reported by GA until it has been disabled, i.e., July 7, 2022, for the reasons explained in the previous section. The new data collected by the internal analytics, from July 10 onwards, will be reported in the next deliverable D7.5.

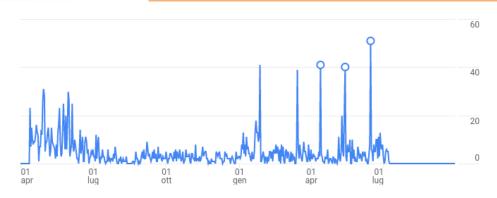

During the first 16 months of the project, the website was accessed by 1750 unique visitors, with about ~20 unique users/day at the beginning of the project, with an expected decrease to ~10 unique users/day after the first 6 months. Figure 2 shows the daily trend. The dates of blog posts, especially from January 2022, are clearly visible and demonstrate the effectiveness and outreach of the blog posts, with an average of ~40 extra unique users/day with a peak of 52 extra unique users/day.

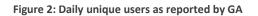

Geographically, the users are mostly distributed among European Union and United States (US). The highest number of unique users is from Italy: this is a direct consequence of the fact that many partners of the consortium are based in Italy (> 500 unique visitors). It is worth mentioning that also from US, even if no partners are based in US, there is a considerable number of unique visitors (> 400 unique visitors). The geographical distribution and evolution are shown in Figure 3.

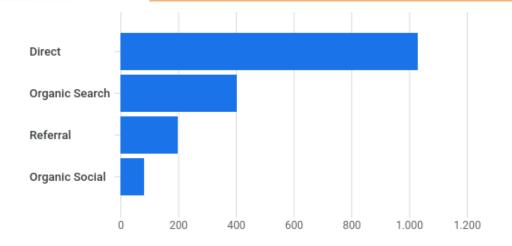

Regarding the referral information of the users, depicted in Figure 4, most of the users come directly typing in the website address. This is the usual effect of the "direct" dissemination activities -- such as presentations, flyers, etc. -- where the website address or qr-code is visible. The second source is from search engines, and then referral from other websites, and social medias.

Figure 4: How the users find the TEXTAROSSA website

Finally, the information on specific pages is shown in Figure 5. Apart from the homepage which is clearly the most visited, the consortium page and the page containing project description are the most accessed. The list of blog posts (News page) is also in the top-5 visited list, including the page describing the TEXTAROSSA co-design approach.

|    | Titolo pagina easse schermata 👻 🕂                                                                                                    | ↓ Visualizzazioni               | Utenti                          |

|----|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|

|    |                                                                                                                                      | <b>5.961</b><br>100% del totale | <b>1.750</b><br>100% del totale |

| 1  | TEXTAROSSA – Towards EXtreme scale<br>Technologies and Accelerators for<br>euROhpc hw/Sw Supercomputing<br>Applications for exascale | 2.167                           | 1.107                           |

| 2  | Consortium - TEXTAROSSA                                                                                                              | 769                             | 385                             |

| 3  | Project Overview – TEXTAROSSA                                                                                                        | 484                             | 307                             |

| 4  | News - TEXTAROSSA                                                                                                                    | 266                             | 168                             |

| 5  | A Co-Design Approach – TEXTAROSSA                                                                                                    | 223                             | 149                             |

| 6  | Work Packages – TEXTAROSSA                                                                                                           | 223                             | 148                             |

| 7  | Page not found – TEXTAROSSA                                                                                                          | 197                             | 197                             |

| 8  | Publications – TEXTAROSSA                                                                                                            | 197                             | 131                             |

| 9  | Press Release and Media Coverage –<br>TEXTAROSSA                                                                                     | 167                             | 100                             |

| 10 | Applications – TEXTAROSSA                                                                                                            | 161                             | 108                             |

Figure 5: Most visited pages (first column shows visits, second column shows unique users)

#### 1.5.3 Social Media

The TEXTAROSSA project has a landing page on three social media: Facebook, Twitter, and Linkedin. The latter is the most accessed by the users. The social networks have been primarily used to promote the website news, event announcements and blog posts. Additionally, the LinkedIn social network has been used to publicize the job offers from the consortium partners.

# 2 Individual Dissemination Plans and Reports

In addition to the dissemination activities performed by the consortium as a whole presented in the previous sections, some partners report the individual dissemination activities and plans for future months of the project in the following sections.

ATOS and InQuattro have only limited dissemination effort and will employ it to participate joint dissemination efforts including joint papers and participation to poster sessions at relevant conferences (e.g. Supercomputing, ...). For the other partners, individual dissemination plan and reports will follow.

### 2.1 ENEA

ENEA participated in several dissemination actions. Among the others, ENEA contributed to the project papers and posters. ENEA presented the TEXTAROSSA project at the SC21 Conference in USA in November 2021, ISC22 Conference in June 2022 and at the EuroHPC19 Coordination Workshop in Madrid (September 2022). The TEXTAROSSA information is delivered on the ENEA websites, among the other the ICT website (www.ict.enea.it). Finally, an ENEA press release was published in 2021.

## 2.2 FHG

Reduced precision and mixed precision floating point operations become more widely accessible on various hardware platforms. If the usability of mixed precision for numerical algorithms can be demonstrated, this would likely create the opportunity to make a submission to a scientific conference or journal.

## 2.3 CINI

CINI leads the dissemination and communication activities. As such, it has set up the website, the social media accounts, and the project communication. Furthermore, CINI presented the paper [1] to the Euromicro Conference on Digital System Design (DSD) 2021 edition and led the writing of the journal extension [2] published by MICPRO. In addition to these joint publications with other partners, CINI published 2 journal articles [3-4] and 11 conference papers [5-10]. CINI also presented the project at the SCADL workshop co-located with IPDPS conference, Lyon, France. CINI further disseminated information about TEXTAROSSA through the flyer at the SAMOS conference 2022.

CINI plans to further disseminate project awareness through several channels, including a workshop at HiPEAC 2023. CINI has also several articles under review, expected to be published in the coming months. In addition, CINI is preparing various future papers submissions and leads the efforts for the joint book proposal in the next period. Furthermore, CINI contributes to the overall dissemination plan by maintaining the website and coordinating the activities for the project blog posts.

## 2.4 INRIA

Inria participated in several dissemination actions. Inria presented the TEXTAROSSA project at the Teratec forum (<u>https://teratec.eu/gb/forum\_2021/index.html</u>) in June 2021. In a very different context, we also presented the project, in relation to the energy minimization issue, to high school students in Libourne (France). The high school students are to take up the elements of our discussion in the framework of an event organized (mid\_November) by the scientific culture center of Bordeaux\_CapScience

(<u>https://www.cap-sciences.net/en/homepage/</u>) in the framework of the COP 27 conference. Finally, we have published several scientific papers related to the optimization of linear algebra kernels.

## 2.5 E4

Paolo Palazzari from ENEA at our booth at #ISC22 to talk about the #TEXTAROSSA Euro-HPC project!

To achieve high performance and high energy efficiency on near-future **#exascale** computing systems, a technology gap needs to be bridged. TEXTAROSSA aims at tackling this gap through applying a co-design approach to heterogeneous HPC solutions, supported by the integration and extension of IPs, programming models and tools derived from European research projects, led by TEXTAROSSA partners.

Know more about TEXTAROSSA https://lnkd.in/eFfFd8xm

#transformingthefuture #isc2022 #hpc #highperformancecomputing

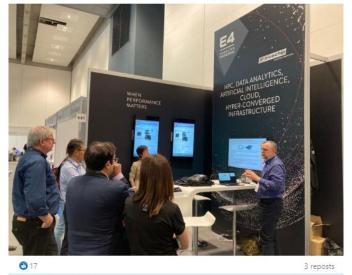

Figure 6: Example of LinkedIn post by E4

For TEXTAROSSA EU project, E4 has done some dissemination and communication activities in 2022.

The first one was during the ISC Supercomputing Event in Hamburg, on May 30th, where E4 hosted at its booth a talk about the project. The talk was run by Paolo Palazzari from ENEA and saw a discrete number of people attending. E4 advertised the talk also in its social media channels, such as the Linkedin with a dedicated post depicted in Figure 6.

On July 6th –  $13^{th}$ , 2022, E4 was sponsor of the ICHEP 2022 Event in Bologna. During the event we showed a poster with all the EU projects we are involved in, including TEXTAROSSA. Daniele Gregori explained attendees the project and our role inside it.

On October 4th  $-6^{th}$ , 2022, we were in BSBF Granada 2022, the event dedicated to Big Science, with a desk and a poster in which we explained TEXTAROSSA among the other projects (same as ICHEP above). During this event Daniele Gregori had a talk where he explained the project and our role inside it.

For the next months we are participating in different events, such as HiPEAC 2023 and ISC 2023 where we will communicate about TEXTAROSSA as well.

### 2.6 BSC

BSC has participated in the dissemination of TEXTAROSSA by participating on the papers published in DSD 2021 and MICPRO 2022, with the description of the plan for implementing the fast task scheduler to be used by the TEXTAROSSA programming models, and the benefits that we have been observing during our developments. BSC did two presentations in the BSC Doctoral Symposium, organized the OmpSs@FPGA PATC course around the use of the OmpSs programming model for FPGA devices, and presented OmpSs@FPGA to researchers at EuroCC.

## 2.7 PSNC

PSNC: UrbanAir application is able to provide weather forecast, assess air quality in urban environments or support renewable energy sources modelling. Therefore, the audience to target are:

- Photovoltaic operators and users

- Distribution system operators

- Companies involved in building and/or running wind farms

- Government institutions

With the recently developed UrbanAir service, reaching target audience shall be easier. Recently, we demonstrated results to one of the largest distribution system operators in Poland, with perspective for future cooperation. Moreover, PSNC will reach stakeholders by participating to HPC conferences such as Supercomputing series.

## 2.8 INFN

During the first phase of the project, we had the opportunity to introduce TEXTAROSSA and specific INFN achievements in several workshops and international conferences. In particular INFN developments in TEXTAROSSA was presented at *TWEPP international conferences* (Title "Progress report on the online processing upgrade at the NA62 experiment", TWEPP 2021 Topical Workshop on Electronics for Particle Physics, virtual edition September 20-24, 2021) with a paper [11] included in the conference proceedings. Furthermore, we gave talks at the *Workshop sul calcolo nell'INFN* (Title "II progetto TEXTAROSSA"; Paestum (SA) May 23-27, 2022) and at workshop *AI@INFN- Artificial Intelligence at INFN* (Title: "APEIRON: a heterogeneous computing platform for real-time inference", Bologna May 2-3, 2022), introducing the application of TEXTAROSSA findings in INFN internal research activities. The TEXTAROSSA ideas and preliminary results were also introduced at the *NVIDIA roundtable meeting* (Cineca Bologna, September 12, 2022) having the opportunity to disseminate our findings in a mixed academic-industrial environment. Finally, we contributed to the first project-wise joint papers, the proceedings of DSD2021 conference [1] and to the derived MICPRO Journal paper [2]. With the advance of INFN research activities in TEXTAROSSA we plan to increase the number of paper submissions to conferences and selected workshops.

### 2.9 CNR

CNR participates to animate the website by news. Furthermore, CNR presented activities developed within TEXTAROSSA at an invited seminar to the dissemination activities of the "Computation-based Science and Technology Research Center (CaSTORC)" of The Cyprus Institute (2021 Summer seminar series), a plenary

invited talk at the Italian National Conference on "Scientific Computing and Mathematical Models" (SCMM 2022), and an invited presentation at the special session on "Large-Scale Models: Numerical Methods, Parallel Computations and Applications" within the 13th International Conference on Large-Scale Scientific Computations (LSSC 2021). Furthermore, CNR contributed to the proceedings paper for Euromicro Conference on Digital System Design (DSD) 2021 and to the journal extension published by MICPRO. In addition to these joint publications with other partners, CNR wrote a paper which is under revision on IEEE on Parallel and Distributed System.

# 3 Individual Exploitation Plans and Reports

The use of results of the TEXTAROSSA project for both commercial purposes and scientific area is key for the project. Exploitation is embedded in the vision of the project. Hence all partners within the project are aware of and committed to the exploitation of the project results.

Moreover, TEXTAROSSA Innovation Manager (IM) will coordinate the exploitation activities among the partners, in close cooperation with the PTC, from the innovative idea to the market, assuring support to overcome issues and providing the fastest and less critical path.

The TEXTAROSSA exploitation strategy comprises the following exploitation activities:

- 1. Refine and detail the identified innovative exploitable results already defined in the proposal

- 2. Complete exploitable results when relevant

- 3. Implement the individual exploitation plan of every partner defined in the proposal

Some partners reported an update of the exploitation plan compared to the original plans described in the Section 2.2.2 of the Grant Agreement. These updates and the individual reports of the exploitation activities follow.

## 3.1 ENEA

During the first half of the project, the ENEA exploitation activities focussed on improving the availability of HPC infrastructures to project partners and beyond the consortium. The main objective is to deliver high level HPC services by exploiting the heterogeneity of HW infrastructures. A special care is for accelerated hardware, among the other FPGAs, since they represent a great opportunity for flexible and energy efficiency hardware.

For what concern projects, ENEA is part of the Italian Centre for HPC with an important commitment in Spoke1 devoted to future HPC technologies.

## 3.2 FHG

The activity in TEXTAROSSA allowed FHG to further develop its Oli&GAS RTM application plus, in collaboration with other partners, to test new technologies like Posit and, as outcomes, there will be new scientific publications (common FHG with CINI-UNIPI contribution at ISC2023) and inputs for further developed to increase the TRL in new EU proposals. The activities on the development of a 16-bit PPU posit processing unit, with CINI-UNIPI, are planned to be exploited in the EPI project.

# 3.3 CINI

CINI, as an academic partner, focuses its exploitation strategy on three main aspects:

- Consolidating its positioning as a leading expert in resource management to secure funding for further research activities in future European calls.

- Technology transfer to either established industrial partners or spin-off companies.

- Exploiting the research carried out to improve its offer of tertiary education targeting Master and Doctoral students.

CINI has identified 3 main innovation products, as reported in the Table 2.2.b of the Grant Agreement. For the first product (Mixed-precision compiler) we defined an open-source exploitation strategy, and it has

#### textarossa

been already licensed under the permissive MIT license: this will allow to cooperate with both academic and industrial partners further development of the toolchain. Commercial exploitation can be still pursued through cooperation agreements with companies to develop support for specific architectural targets. For the remaining two innovation products (Posits Processing Unit and Crypto accelerator for secure HPC services), discussions are ongoing regarding the licensing model as there is opportunity to pursue licensing agreements for hardware components or to release such components as open hardware.

The activity in TEXTAROSSA allowed CINI-UNIPI as main exploitable result to further develop its posit technology (C++ Posit library and IPs) thanks to the development of light posit processing unit (useful for data compression of CNNs) and full posit processing unit (for compression and AI computation) and its integration with RISC-V cores. The developed IPs lead to rise of collaborations with other partners (being used by CINI-POLIMI, INFN, FHG) with publications in journals and top HPC conferences (e.g. ISC2023, HIPEC2023, Conga2023 part of AsiaSiupercomputing2023), contribution to enrich PhD and MS thesis offer at UNIPI, strength the position of UNIPI in the European scenario since UNIPI is entering as a key partner for digital IPs in the most important HPC new proposals, such as RISC-V FPA, EPI2, Italian HPC national center. The activities on the development of a 16-bit PPU posit processing unit, with FHG, are planned to be exploited in the EPI project.

Concerning part of the activities carried out by CINI-POLIMI, depending on the final project results, it will be analysed the possibility of a partnership for the improvement and licensing of a thermal control strategy tailored for the two-phase cooling.

As a notable early exploitation results of the project, CINI-UNITO will purchase a server based on the TEXTAROSSA technology, a system provided by E4 with 4 NVIDA H100 GPUs and exploiting the two-phase cooling provided by InQUATTRO. This platform will be located in the green datacenter of CINI-UNITO for deep testing with the existing commercial users and to foster further scientific cooperation with the project partners.

### 3.4 INRIA

During the first half of the project, the exploitation activities of Inria focus on improving StarPU and porting some of the Chameleon and ScalFMM to kernels on FPGA. Both will be connected in the second part of the project to enhance StarPU, Chameleon and ScalFMM. We will also try to make our scheduler generic to be used by any type of application.

# 3.5 ATOS

Studying the two-phase liquid cooling technology in close connection with InQuattro and other preliminary users will accelerate the implementation on OpenSequana blades and the feedbacks to the technology providers, so that this technology is potentially improved and takes into account industrialization constraints as early as possible. The OpenSequana blade prototype selected to evaluate the two-phase liquid cooling will be an ATOS product. The cooling adaptation developed in this project will provide an evaluation of the cooling technology in real conditions with the last generation on powerful accelerators. Nevertheless, a further optimization will be required to densify the solution and potentially adapt the rack itself to this innovative cooling solution.

During the first period of the project, Atos kicked-off the study of the two-phase liquid cooling technology. Furthermore, the preparation of the prototype (IDV-A) based on different types of GPU was carried out: a comparison study with pros and cons on the GPU Nvidia and GPU Intel was realised. By the way, both types of GPU are in an early stage of general availability at the suppliers.

This study was presented to the project partners. After discussions with the project partners, a decision was made, the project has decided to have Nvidia GPU to equip the prototype. This work is still ongoing in the second period of the project to prepare a prototype based on Thermal Test Vehicles before the GPU components are available, and then prepare the prototype with GPU. This prototype will be a component of the envisioned exploitable result from Atos.

The prototype of blade equipped with the 2-phase liquid cooling will be implemented in a new Atos HPC Rack, a part of the Atos HPC offers, if the analysis made in the TEXTAROSSA project demonstrates this cooling technology is more efficient than the current Atos DLC technology.

#### 3.6 E4

During the first half of the period, E4 began to study which server met the design constraints defined in the proposal phase and in the subsequent analyses of WP3, WP5, identifying the most suitable one among different commercial proposals.

Through a joint work with the partners, through virtual meetings, the accelerators based on FPGA technology were then chosen. Currently the server based on ARM technology and Xilinx FPGA accelerators is available at the E4 laboratory for remote access by the partners. The two-phase cooling system developed in collaboration with InQuattro will be applied to this server in the next months. At the end of the project, if the energy improvement parameters are verified, the system will be part of the commercial proposal of E4.

## 3.7 BSC

BSC has delivered the seminar on OmpSs@FPGA on March 25, 2022, and plans to keep doing this type of seminar for researchers interested in computing using FPGA platforms. Regarding exploitation of results in research projects, we are providing the fast task scheduler to EPI SGA2, and MEEP projects, to be used as part of the hardware scheduler in RISC-V environments.

## 3.8 PSNC

In the first period of project, the PSNC exploitation activities focused on UrbanAir application. We started to develop an online service with weather prediction and air quality forecasts to support different stakeholders – environmental institutions to control air quality, distribution network operators to maximise production from renewable energy sources, government institutions to support urban planning. At first, dissemination aimed at Polish national distributed system operators.

## 3.9 INFN

During the first period of project, the exploitation activities of INFN focused on the integration of our inter-FPGA low-latency communication IP with the HLS toolchains in HEP experimental initiatives. Contacts and dissemination activities towards our reference science community (HEP Experiments) led to the demonstration of a first prototype of a ML architecture FPGA-based for Cherenkov ring identification of the CERN NA62 experiment RICH detector [11].

Contacts with other HEP experiments, that can leverage on TEXTAROSSA-designed low latency communication IP to move data between different interconnected FPGA, are ongoing. We plan to finalise additional exploitations in HEP framework before the end of project.

In addition, we are exploring the opportunity to licence the communication IPs for industrial exploitation, supported by the INFN Transfer Technology office.

## 3.10 CNR

During the first period, CNR hired two young collaborators and started to design and implement first version of the Math-lib for parallel sparse matrix computations. Some work to test the library kernels is ongoing, some presentations at national events and some working papers are also in progress. Participation to the TEXTAROSSA project was an added value to be invited to collaborate to the dissemination activities of the Computation-based Science and Technology Research Center (CaSTORC) of The Cyprus Institute acting as the Nation HPC Competence Center for Cyprus, and to lead a WP in a new project proposal for the EuroHPC call for Center of Excellence on Supercomputing Applications.

## 3.11 InQuattro

During the first half period of the project, In Quattro has begun to study and to develop the application of the two-phase cooling technology for HPC servers (the two nodes provided by Atos and E4). The activities were focused not only to develop the technical solutions (design and testing, as described in Deliverable 3.2), but also to understand and to collect the needs of users and stakeholders. The latter point is important to reach a final solution with high potential to be successful in the market. In the present project several types of users and stakeholders are present: E4 and Atos (potential customers of the two-phase cooling systems), several universities and research institutions (end users of the hardware equipment). Direct discussions with Atos and E4 have been carried out to define the requirements of the cooling systems in relation with the selected hardware. These discussions have been valuable to understand not only the technical requirements, but also to understand "why" of these requirements. Same approach has been used to understand the "why" of the final users of the HPC systems with direct discussions with some partner and during the ISC event in Hamburg in June 2022. All these information and inputs result in the definition of the first prototypes of the two-phase cooling system for HPC servers. During the second part of the project, when the two-phase cooling system works on the servers, this activity will continue in order to collect feedback, suggestions, criticisms (few, hopefully) with the objective to refine and improve the design of the prototypes of the two-phase cooling systems.

## 4 Products and IPs

In the following sections, for each partner, we propose a possible characterization table for main products/IPs developed or improved in the TEXTAROSSA project. These tables are useful to identify the innovations and exploitable results of the project.

#### 4.1 ENEA

| Innovation                     | FPGA ImgLib                                                                                                                                                                                                                                                                                                                                   |         |                                    |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------|

| Problem                        | How to perform high-performance image processing on FPGA.                                                                                                                                                                                                                                                                                     |         |                                    |

| Alternative<br>solutions       | Xf::OpenCV                                                                                                                                                                                                                                                                                                                                    |         |                                    |

| Innovation of<br>your solution | Kernels are optimized for variable bithwidths, so can be easily adapted to the available I/O bandwidth.                                                                                                                                                                                                                                       |         |                                    |

| Description                    | Implemented several operators for image and stream processing (color space conversion, splitting and merging of image components, FIR filtering, median filtering, histogram equalization, various image generation and mixing, single pixel transformation, rotation, resizing, zooming, stream splitting, stream copying, stream merging,). |         |                                    |

| IPR & License                  | Open Source                                                                                                                                                                                                                                                                                                                                   |         |                                    |

| TRL                            | At the beginning of the project                                                                                                                                                                                                                                                                                                               | Current | Expected at the end of the project |

|                                | 0                                                                                                                                                                                                                                                                                                                                             | 2       | 4                                  |

| Availability                   | Not yet defined                                                                                                                                                                                                                                                                                                                               |         |                                    |

| Reference<br>Person            | Paolo Palizzari <paolo.palazzari@enea.it></paolo.palazzari@enea.it>                                                                                                                                                                                                                                                                           |         |                                    |

| Possible market                | Image processing                                                                                                                                                                                                                                                                                                                              |         |                                    |

#### 4.2 CINI

| Innovation               | TAFFO for CUDA and OpenCL                                                                                               |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| Problem                  | Support Mixed-Precision computing on heterogeneous platforms leveraging GPGPUs, programmed using either OpenCL or CUDA. |  |

| Alternative<br>solutions |                                                                                                                         |  |

| Innovation of<br>your solution | The proposed solution enables automated management of computation precision, thus reducing the burden on the application developer.                                                                                                                                                                    |                               |         |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------|

| Description                    | TAFFO is a set of plugins for the LLVM compiler framework to perform precision tuning (both in terms of short floating point data types and of integer/fixed point data types). The innovation provided by TEXTAROSSA enables the plugins on the main commercial GPGPUs by supporting CUDA and OpenCL. |                               |         |

| IPR & License                  | POLIMI, permissive open so                                                                                                                                                                                                                                                                             | ource (MIT)                   |         |

|                                | At the beginning of the<br>projectCurrentExpected at the end of the<br>project                                                                                                                                                                                                                         |                               |         |

| TRL                            | •••                                                                                                                                                                                                                                                                                                    | Current                       |         |

| TRL                            | •••                                                                                                                                                                                                                                                                                                    | Current<br>4                  |         |

| TRL<br>Availability            | project<br>3                                                                                                                                                                                                                                                                                           |                               | project |

|                                | project<br>3<br>- Publicly available:                                                                                                                                                                                                                                                                  | 4<br>https://github.com/TAFFO | project |

| Innovation                     | Thermal control policy for evaporative cooling                                                                                                                                                                                                                                                                        |   |   |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|--|

| Problem                        | Manage temperature of computational devices when using evaporative cooling.                                                                                                                                                                                                                                           |   |   |  |

| Alternative<br>solutions       | Currently, no solution exists to jointly control on-chip operating frequencies and evaporative cooling flow rate.                                                                                                                                                                                                     |   |   |  |

| Innovation of<br>your solution | The proposed solution enables efficient use of evaporative cooling solution for HPC systems.                                                                                                                                                                                                                          |   |   |  |

| Description                    | The proposed cooling solution is a hierarchical control policy that acts on a fast actuator (DVFS) that however incurs a performance penalty when used, and a slow actuator (coolant flow rate) that has no performance penalty, to improve computational performance without over-provisioning the cooling capacity. |   |   |  |

| IPR & License                  | POLIMI, proprietary                                                                                                                                                                                                                                                                                                   |   |   |  |

| TRL                            | At the beginning of the<br>projectCurrentExpected at the end of the<br>project                                                                                                                                                                                                                                        |   |   |  |

|                                | 1                                                                                                                                                                                                                                                                                                                     | 2 | 4 |  |

| Availability                   | Deliverable D3.5                                                                                                                                                                                                                                                                                                      |   |   |  |

| Reference<br>Person | Federico Terraneo <federico.terraneo@polimi.it></federico.terraneo@polimi.it>         |

|---------------------|---------------------------------------------------------------------------------------|

| Possible market     | CPU manufacturers, GPU manufacturers, FPGA manufacturers, HPC equipment manufacturers |

| Innovation                     | First production deployment of a CPU+GPU server with a two-phase cooling system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                    |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------|

| Problem                        | Power saving in existing HPC datacentres (retrofit).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                    |

| Alternative<br>solutions       | Today the market of two-phase cooling is very small, the other only player selling servers with two-phase cooling (zutacore) does not support CPU+GPU servers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                    |

| Innovation of<br>your solution | The solution is suitable for cooling servers with GPUs; to our knowledge, there are<br>no other solutions on the market. We plan to demonstrate that it is possible to run<br>servers with full-power Nvidia H100 GPUs (700W per GPUs) on air-cooled data<br>centres, which can be crucial for small-medium-sized data centres.                                                                                                                                                                                                                                                                                                                                                           |   |                                    |

| Description                    | Supermicro server with 2 Intel sockets and 4 Nvidia H100 SXM modified (by E4) with<br>a 2-phase cooling system from InQuattro. The system will be integrated within the<br>UNITO's cloud-HPC system (https://hpc4ai.unito.it/documentation/) and made<br>available via UNITO's integrated cloud-HPC management system based on the<br>StreamFlow cloud-HPC management system (https://streamflow.di.unito.it) and<br>Jupyter-workflow (https://jupyter-workflow.di.unito.it). StreamFlow and Jupyter-<br>workflow development has been funded by EuroHPC project. Streamflow was<br>selected in April 2023 by EU Innovation Radar program<br>(https://www.innoradar.eu/innovation/49626). |   |                                    |

| IPR & License                  | Solution commissioned and funded by UNITO, integrated by E4 with cooling system made by InQuattro.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                    |

| TRL                            | At the beginning of the<br>projectCurrentExpected at the end of t<br>project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | Expected at the end of the project |

|                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 | 8/9                                |

| Availability                   | http://hpc4ai.unito.it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                    |

| Reference<br>Person            | Marco Aldinucci <aldinuc@di.unito.it></aldinuc@di.unito.it>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                    |

| Possible market                | Existing cloud-HPC datacenters (120-250KW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                    |

## 4.3 INRIA

| Innovation |

|------------|

|------------|

| Problem                        | How FPGA can be efficiently used in a dynamic task-based runtime system                                                          |                         |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| Alternative<br>solutions       | OmpSs@FPGA (also exploited in TEXTAROSSA)                                                                                        |                         |  |  |

| Innovation of<br>your solution | Technical upgrade of StarUP.                                                                                                     |                         |  |  |

| Description                    | FPGA are managed as any other PU and thus can compute tasks provided by the users.                                               |                         |  |  |

| IPR & License                  | LGPL-2.1 license (same of StarPU)                                                                                                |                         |  |  |

| TRL                            | At the beginning of the<br>projectCurrentExpected at the end of the<br>project                                                   |                         |  |  |

|                                | 3 4 5                                                                                                                            |                         |  |  |

| Availability                   | Publicly available online: https://starpu.gitlabpages.inria.fr/                                                                  |                         |  |  |

| Reference<br>Persons           | Hayfa Tayeb <hayfa.taybe@inria.fr>, Bérenger Bramas <berenger.bramas@inria.fr></berenger.bramas@inria.fr></hayfa.taybe@inria.fr> |                         |  |  |

| Possible market                | No market directly, but thr                                                                                                      | ough the use of StarPU. |  |  |