# ENEA

### Atos CINECA (nría

# The TEXTAROSSA Project: Cool all the Way Down to the Hardware

**Antonio Filgueras (BSC)**

DSD 2024, Paris, France

#### **Partners**

PSNC Fraunhofer Atos université BORDEAUX POLITECNICO UNIVERSITÀ DEGLI STUDI DI TORINO Barcelona Supercomputing Center ERSITÀ DI PISA En CINEC INFN Intitute Nazionale di Fisica Nucleari DUATTRO

- 11 partners

- 6 linked institutions

- 5 countries

- Lead by Massimo Celino (ENEA)

### **Project Motivation**

- Performance and energy efficiency remain main HPC challenges

- Users are in demand of higher performance

- Power often limits the available performance

- Heterogeneous systems try to address these challenges

- Increased complexity

- Large knowledge gap with domain experts

# **Objectives**

- Increase performance while keeping energy bounds

- Hardware stack redesign

- Infrastructure improvements (2-phase cooling and thermal management)

- Experimental Hardware platforms (GPU and FPGA based)

- Software stack redesign

- Use application-specific accelerators

- Efficient multi-device and multi-node runtime support

- Lower the entry barrier for new users to heterogeneous HPC systems

- Provide a set of application-specific IP blocks for different tasks

- Develop tooling for leveraging these IPs

- Provide tools for resource management

#### Hardware prototypes

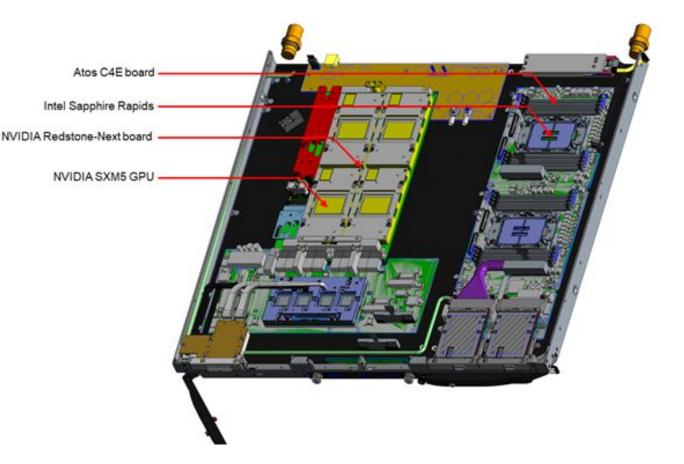

# Hardware platforms: IDV-A

- Developed by Atos

- 4 Nvidia H100 GPUs

- 2 Intel Xeon 8470 CPUs (2x54 cores)

- 2-phase cooling system

- >3500W Thermal Design Power

# Hardware platforms: IDV-E

- Developed by E4 (based on Ampere Mt.Collins)

- 2 Ampere Altra Max CPU (2x128 ARMv8 cores)

- 2 AMD Alveo U280 Accelerator cards

- 2-phase cooling system

- 950W TDP

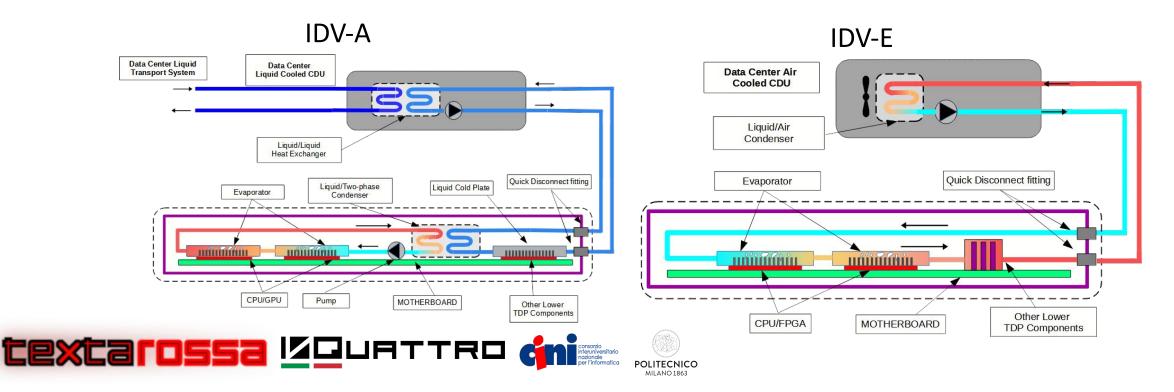

# **Evaporative Cooling (two-phase cooling)**

- Use fluid phase change for energy exchange

- Electronic device cooling (evaporation)

- Waste heat reject (condensation)

- Impact on thermal control strategies

## **Thermal Management**

- Thermal control prevents ICs (CPUs, GPUs, FPGAs) from burning

- Use Dynamic Frequency and Voltage Scaling to reduce power (and heat)

- Heat spikes are quick (~10ms)

- Cooling actuators (pumps, fans) have to adapt to load changes

- Power actuators (DVFS) need to take into account thermal mass and actuator inertia

- Fan vs. pump, heatsink vs. block + fluid, etc.

- Transient models of the evaporative cooling loop have been developed

- Hierarchical thermal controller has been designed

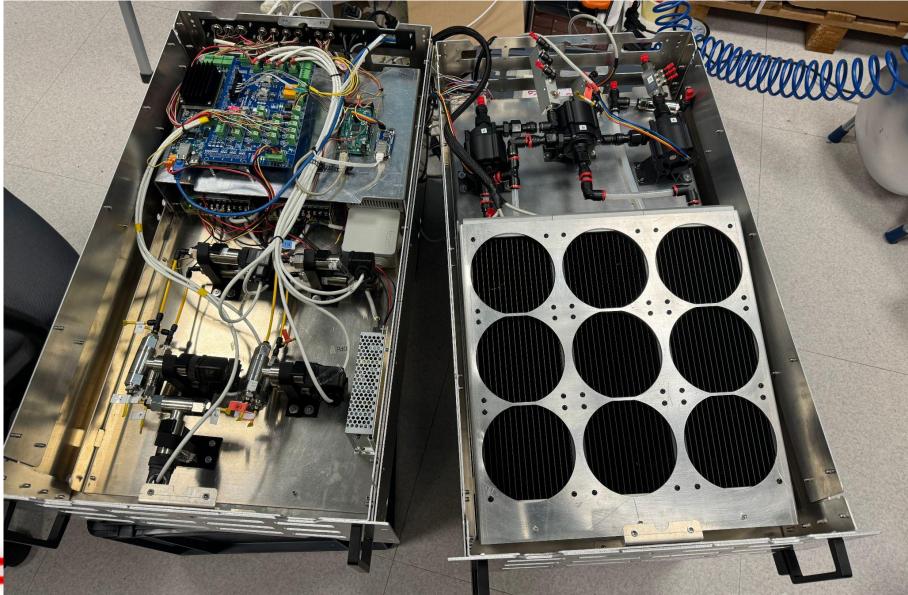

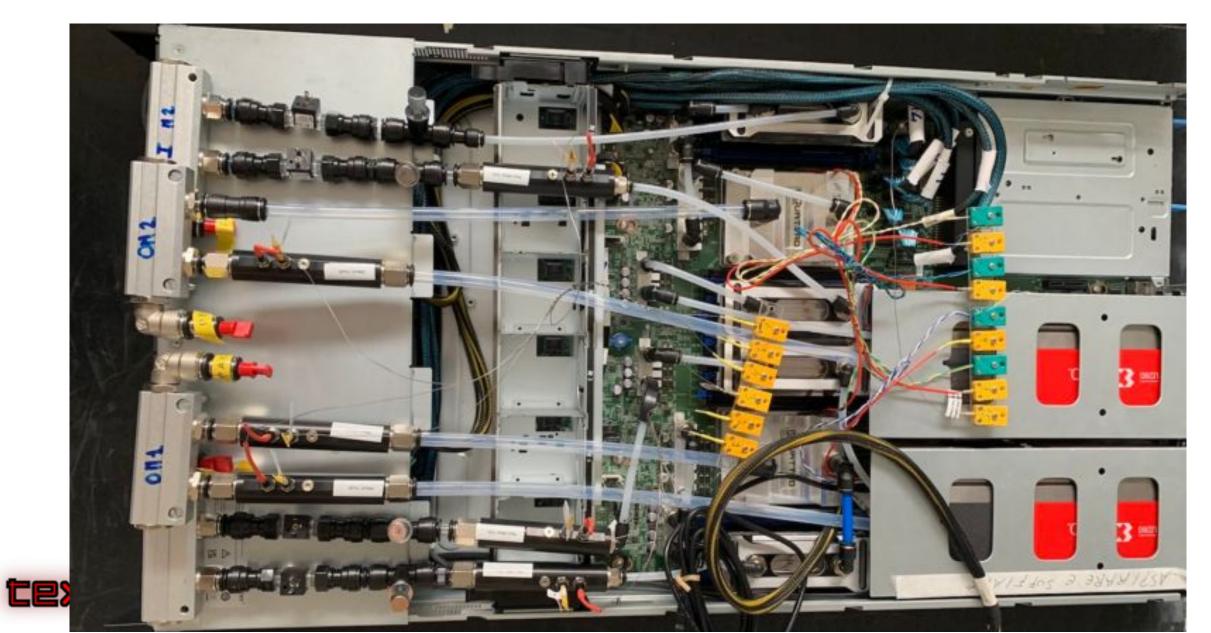

### **IDV-A Prototype**

### **IDV-A Prototype**

#### **IDV-A Prototype**

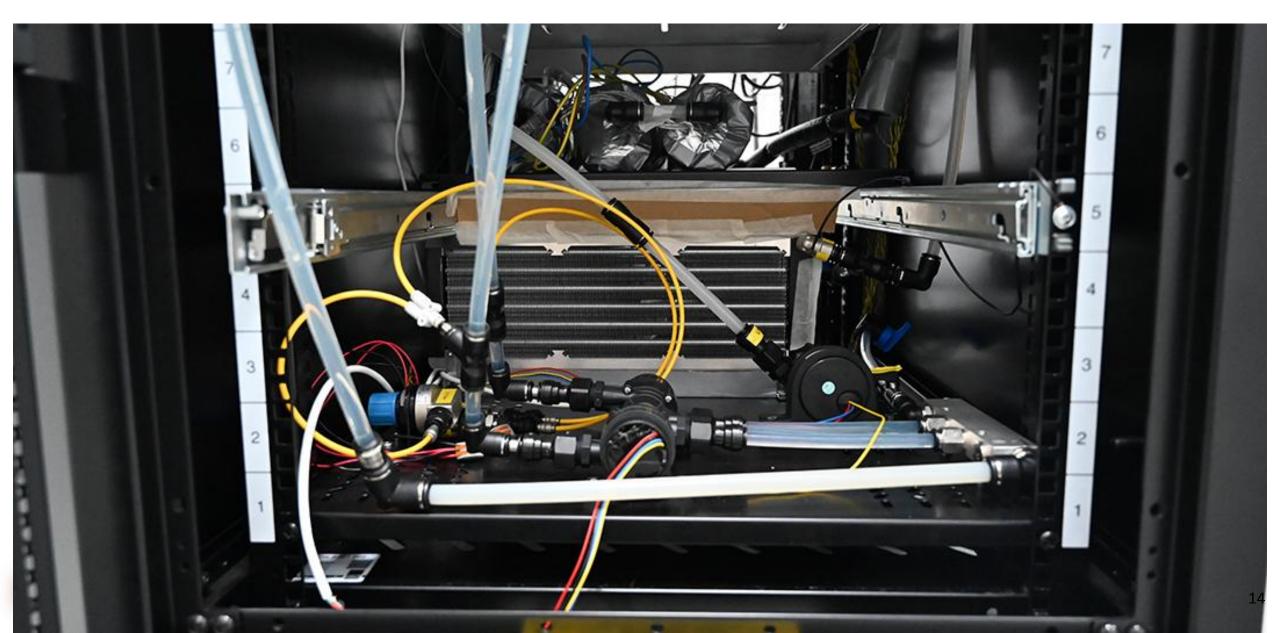

### **IDV-E Prototype**

## **IDV-E Prototype**

### **IP project contributions**

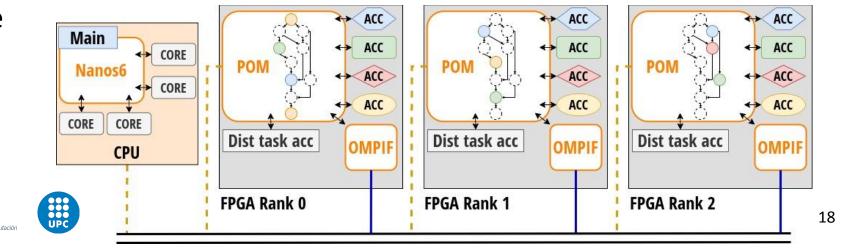

#### **OmpSs@FPGA**

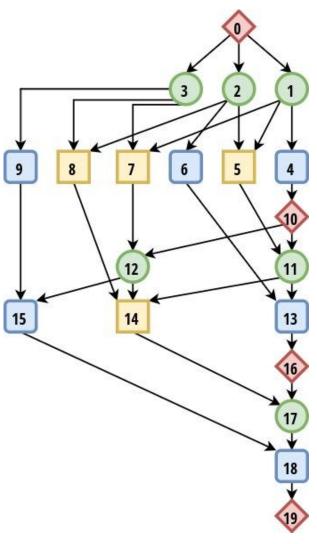

#### OmpS-2 task-based programming model

#### Task graph

#### Cholesky source code

```

void cholesky_blocked(const int nt, float *A[nt][nt])

{

for (int k = 0; k < nt; k++) {

#pragma oss task inout(A[k][k])

potrf( A[k][k] );

for (int i = k+1; i < nt; i++) {</pre>

#pragma oss task in(A[k][k]) inout(A[k][i])

trsm( A[k][k], A[k][i] );

for (int i = k+1; i < nt; i++) {</pre>

for (int j = k+1; j < i; j++) {</pre>

#pragma oss task in(A[k][i], A[k][j]) inout(A[j][i])

gemm( A[k][i], A[k][j], A[j][i] );

#pragma oss task in(A[k][i]) inout(A[i][i])

syrk( A[k][i], A[i][i] );

```

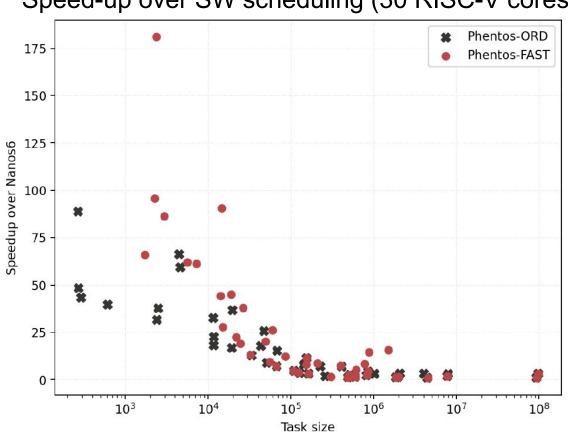

# **Hw IP for Task Scheduling**

A HW Fast Task Scheduler IP allows OmpSs@FPGA and many-core nodes to • schedule tasks with negligible overhead

- In many-core RISC-V nodes results in over 100x speedup in task scheduling

- In OmpSs@FPGA allows near perfect scalability (as shown later)

Speed-up over SW scheduling (30 RISC-V cores)

## **OMPIF: OmpSs MPI for FPGA**

- MPI-like API called from the FPGA code → OmpSs MPI for FPGAs (OMPIF)

- OMPIF hardware runtime handles calls to the API

- FPGA-to-FPGA communication

```

void OMPIF_Send(const void* buf, int size, int dest, int tag)

void OMPIF_Recv(void* buf, int size, int source, int tag)

void OMPIF_Allgather(void* data, unsigned int size);

void OMPIF_Bcast(void* data, unsigned int size, int root);

int OMPIF_Comm_rank();

int OMPIF_Comm_size();

```

Distributed task: Special type of task used to start the application on all FPGAs.

textaross

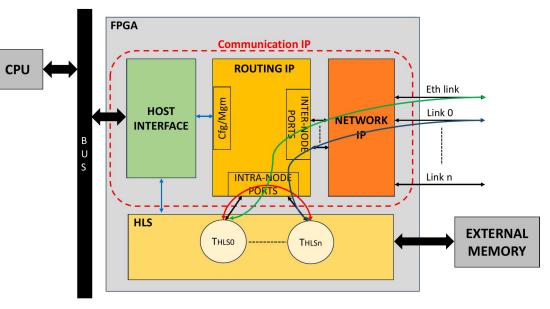

#### **APEIRON: Low-Latency FPGA communication**

- Communication between kernels in the same or different device

- 3D mesh routing

- HLS kernel interface

#### Kernel API

#### **IP** Architecture

### Results

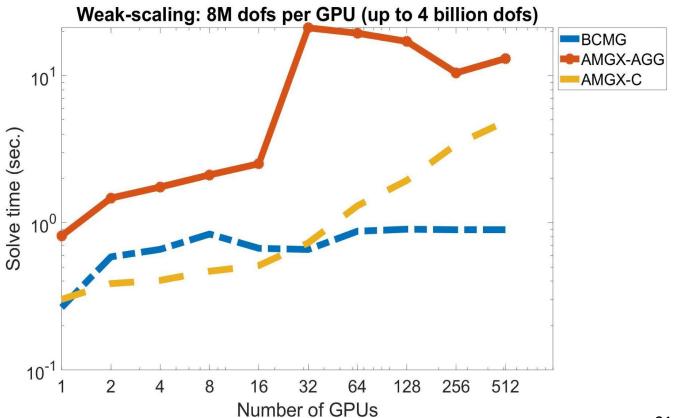

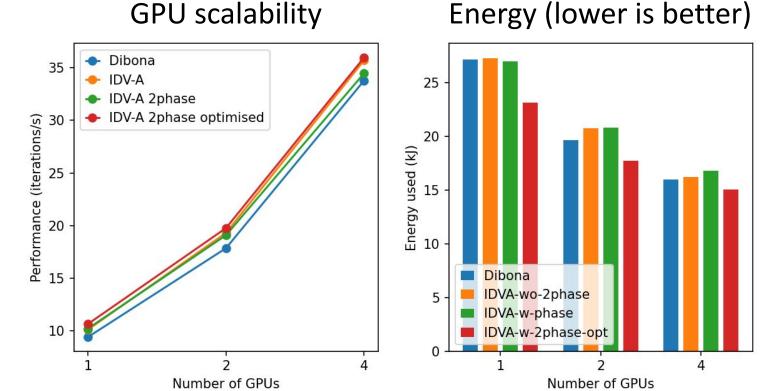

# Math library (IDV-A)

- A communication-reduced CG solver for extreme-scale sparse linear systems on GPU-accelerated supercomputers

- An innovative AMG preconditioner (BCMG) developed in Textarossa shows significative benefits if compared with the state of the art (Nvidia AmgX library) on a HPCG-like benchmark

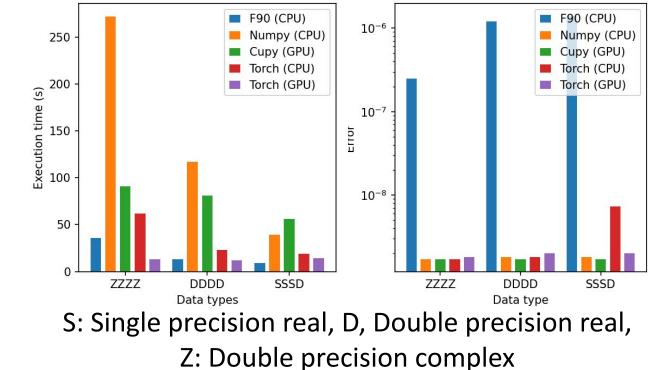

#### **TAFFO**

- A suite of compiler passes integrated with LLVM to automatically tune the computation precision.

- Employs value range analysis from input data ranges provided by the programmer via attributes

|                | Resnet50 |      | Renet101 |      | Accuracy (%)<br>Resnet152 |      | VGG16 |      | VGG19 |      |

|----------------|----------|------|----------|------|---------------------------|------|-------|------|-------|------|

| Numeric format | top1     | top5 | top1     | top5 | top1                      | top5 | top1  | top5 | top1  | top5 |

| p16e2          | 57       | 75   | 60       | 77   | 61                        | 80   | 55    | 73   | 52    | 74   |

| p8e2 (mixed)   | 39       | 58   | 36       | 59   | 45                        | 61   | 49    | 72   | 46    | 65   |

| fp16 (e5m10)   | 48       | 67   | 52       | 76   | 43                        | 65   | 54    | 74   | 53    | 73   |

| fp32 (e8m23)   | 56       | 76   | 59       | 79   | 61                        | 80   | 54    | 74   | 53    | 74   |

#### Imagenet V2 classification accuracy with different precisions

TAFFO allows fast tuning of NN precision requirements

# Quantum TEA (IDV-A)

Quantum TEA simulates quantum systems using Tensor Network Models

Via precision tuning of the different layers of the TNM we can obtain performance gains while maintaining precision

Istituto Nazionale di Fisica Nuclear

#### Precision tuning (lower is better)

23

# UrbanAir (IDV-A)

• Predicts air quality in in complex urban areas using a multi-scale model

• Parallelized using cuda

- 11% higher performance (IDV-A vs. Dibona)

- 25% further improvement by using mixed precision

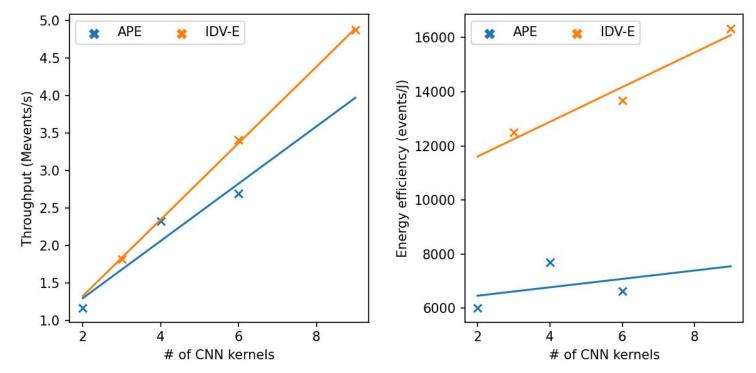

# **Raider/APEIRON (IDV-E)**

Predict the number of charged particles in each RICH detector physics event (@10MHz) using a CNN on FPGA

- Distribute processing across multiple FPGA

- Use APEIRON for low-latency communications

#### Performance and energy efficiency (higher is better)

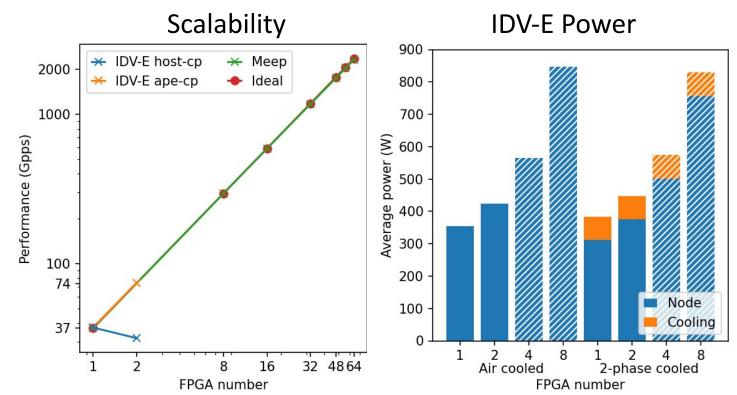

# Nbody/OmpSs (IDV-E)

• Simulate gravitational interactions between particles

- Distributed processing using OmpSs@FPGA & OMPIF

- Near-ideal scalability in large number of nodes

- Energy efficiency improvements due to cooling technology

## Conclusions

- Two-phase cooling is a new reliable and sustainable solution for effective thermal management of exascale systems.

- It is feasible to effectively reject heat in warm climates without using chillers or cooling towers

- Thermal management has a big impact on energy efficiency

- Algorithm redesign is often required to exploit large scale complex architectures

- Developer tools (programming models and toolchains) are key

- Multi-FPGA architectures are interesting for particular workloads

- Fast inter-FPGA communication is needed

- Programmability is still an issue

- Two-phase cooled IDV-A and IDV-E provide a starting point for greener HPC

# ENEL

## Atos CINECA Ínría

# The TEXTAROSSA Project: Cool all the Way Down to the Hardware

antonio.filgueras@bsc.es Coordinator: massimo.celino@enea.it <u>textarossa.eu</u>