Project results

The following objectives of the project have been addressed by applications and use cases:

- Energy efficiency: increase the energy efficiency by 2-5x compared with current available HPC solutions based on CPU or CPU+GPU thanks to:

- New energy-efficient processors and accelerators

- Integrated use of FPGAs

- Bi-phase cooling

- Mixed-precision and data compression techniques

- Direct communication between FPGAs

- Sustained application performance: increase in performance by 2-10x compared with current solutions based on CPU or CPU+GPU thanks to:

- new AI accelerators and high-performance GPUs and FPGAs

- HW fast schedulers

- low-latency inter-/intra-node links

- better cooling allowing higher frequencies

- fast flow enabled at programming mode and run time levels

- Optimization of applications

- Seamless integration of reconfigurable accelerators

- TEXTAROSSA vendors will adopt tools and solutions of the project.

- Integrated Development Platforms (IDVs)

- Development of new IPs

- IDV-A – GPU

- IDV-E – Reconfigurable technology

- Fine-tuned thermal policies integrated with an innovative cooling technology

- Positioning in the HPC market of the integrated cooling technology.

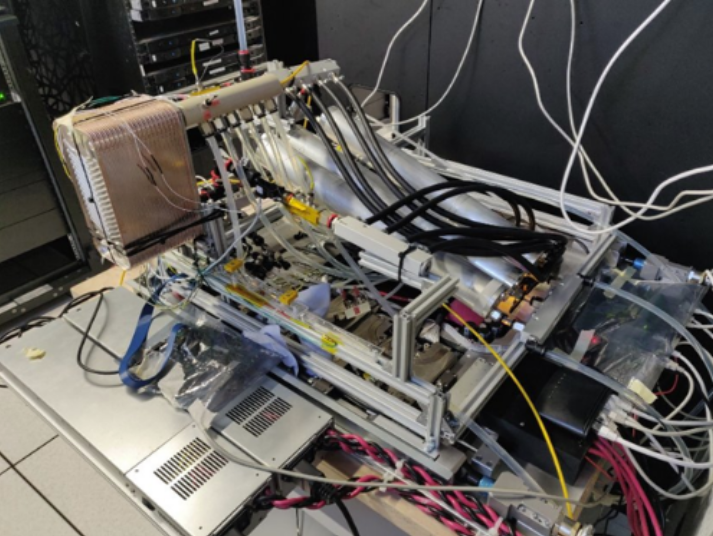

- Deployment of two heterogenous nodes featuring cutting edge hardware and refrigerated by the innovative two-phase cooling system

- IDV-E: ARM + FPGA (U280): 950W TDP

- IDV-A: Intel Xeon + NVIDIA H100: Open Sequana – 3.5 KW TDP

|

|

| IDV-E with two-phase cooling |

IDV-A with two-phase cooling |

Seamless integration of reconfigurable accelerators

Goal: integration of FPGA-based accelerators

Means: VitisHLS extensions: APEIRON, OmpSs@FPGA, Fastflow, TAFFO

Achievements:

- APEIRON: validated on IDV-E + RAIDER and FIPLib

- OmpSs@FPGA: validated on IDV-E

- Fastflow: integrates deployment of kernels developed with VitisHLS

- TAFFO: developed support for VitisHLS to perform mixed precision computing in generated accelerators

|

Fine-tuned thermal policies integrated with an innovative cooling technology

Goal: validated hierarchical thermal control

Means: 2-phase cooling on IDVs, thermal control policies

Achievements:

- TRL 7 validation of InQuattro 2-phase cooling technology

- Commercial product from E4 based on X86+GPU+ 2-phase cooling

- DVFS inner control loop + coolant flow rate outer control loop

- Temperature within 1° of target set point for GPU

- Temperature within 2° of target set point for 104 core

|

For further details please check the deliverable D6.3.